3D NAND闪存“卷”到1000层 可靠性挑战凸显

来源:爱集微 时间:2024-12-19

芯片行业正努力在未来几年内将3D NAND闪存的堆栈高度提高至四倍,从200层增加到800层或更多,利用额外的容量将有助于满足对各种类型内存的无休止需求。

这些额外的层将带来新的可靠性问题和一系列增量可靠性挑战,但近十年来,NAND闪存行业一直在稳步增加堆栈高度。2015年,东芝宣布推出首个使用硅通孔的16芯片堆栈,这实现了更高的带宽、更低的延迟和更快的I/O,同时也为堆叠其他类型的内存和逻辑芯片铺平了道路。

“最初,NAND是水平扩展的,”Lam Research(泛林集团)蚀刻生产力和设备情报副总裁Tae Won Kim表示,“但10多年前,制造商意识到横向扩展本身并不具有成本效益,因此他们转向了垂直扩展。”

堆叠芯片为显著提高密度和加快数据访问速度打开了大门。ACM Research(盛美半导体)总经理Mohan Bhan表示:“3D NAND的发展方向是500到1000层,但实现这么多层并非仅仅靠做更多我们一直在做的事情就能实现。”

主要的传统工艺问题与高纵横比(HAR)蚀刻和沉积有关,以确保所有这些层中的字符串一致且无空隙。由于多晶硅通道的总电阻增加,通道高度也对读取电流构成挑战。因此,一些开发人员正在转向使用混合键合的双晶圆解决方案,但这些改进只能到此为止。

Brewer Science业务发展经理Daniel Soden表示:“虽然尖端制造商始终致力于增加层数,但层的额外扩展/堆叠受到蚀刻预算和图案化挑战等因素的限制。”

但是达到1000层的最快的方法,也许是唯一的方法将是串堆叠。

业界提出增加内存容量的方法

业界确实有办法在不增加更多层的情况下增加内存容量。泛林集团的Kim表示:“NAND制造商不仅可以垂直扩展,还可以横向和逻辑扩展。”

逻辑缩放增加了单个闪存单元中存储的位数,而横向缩放则减少了单元之间的间距。此外,研究人员正在尝试将列一分为二,使单元总数增加一倍。各种想法都在发挥作用,但效果将是降低间距并在相同区域存储更多数据。“缩放这种电荷陷阱架构的间距是提高设备上电容器密度的好方法,而无需进一步增加层数。”Brewer的Soden说。

另一个容量提升的方法涉及将更多数据装入单个单元。在一个单元中存储多个位元并不是一个新想法。各公司正在推出每单元两位的多层单元(MLC)、三层单元(TLC)和四层单元(QLC)。开发人员现在正在接近每单元五层(五层单元或PLC)。管理如此微小的电荷状态差异(31个级别加上空)的算法可能会更复杂,纠错也是如此,因此性能可能会受到影响。

目前,PLC的实现方式以及陷阱氧化物的成分尚不明确,一些研究表明,浮栅可能成为更好的PLC单元。甚至有人在研究六层单元(HLC),每个单元存储六位。然而,这仍在研究中。

SK海力士有一种方法可以将存储单元分成两个三比特单元,总共六比特。七比特存储单元已经在低温下进行测试,以降低噪音并提高读取保真度。

保持均匀的层次

堆叠3D NAND的基本优势在于,只需一个光刻步骤即可获得数百层,从而对所有层进行图案化。缺点是钻孔变得更加困难,尤其是当高深宽比接近100:1时。

让每层变薄似乎有利于增加层数,而不会使堆栈太高。“层厚度在150到100埃的范围内。”Bhan说。但字线层变薄会使它们的电阻变大,从而损害性能。一些研究人员正在探索用电阻更低的钌或钼代替钨金属。但对于产品开发来说,层厚度目前保持不变。

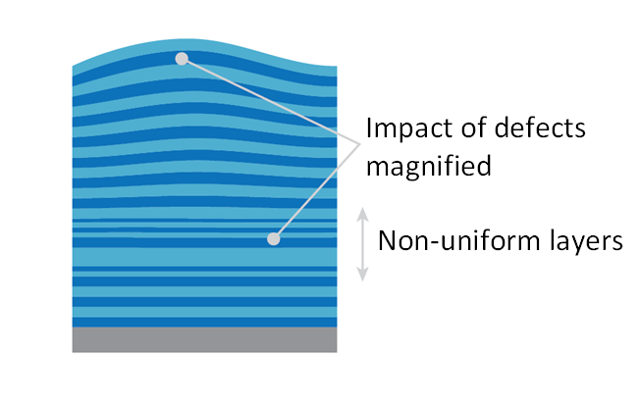

挑战不仅仅在于蚀刻,在保持良好平面度的同时添加额外的层更难。以前可以忽略的小错误现在累积起来,使得它们在更高的堆栈顶部变大而无法忽略。

堆栈最初由交替的SiO2和S3iN4层组成,但氮化物最终将被移除并替换为栅极金属。在每一代中,随着堆栈层数的增加,重点仍然是保持各层尽可能均匀。可以容忍轻微的错误,但随着堆栈层数的增加,这些错误往往会成倍增加,这意味着每一代都必须更加努力地提高平面度。

图1:3D NAND堆栈的平面性和均匀性较差。来源:盛美半导体

在沉积过程中旋转晶圆是盛美半导体用来提高平面度的一项技术。随着沉积的进行,该公司的设备会定期抬起晶圆并将其旋转180°,就像足球队每节改变方向一样。“沉积过程中对晶圆旋转的要求以及整个过程的均匀性将非常重要。”Bhan说。

上一篇: 美国国防部将中微公司及IDG资本移出制裁清单 下一篇: 美国要求英伟达调查其芯片如何流入中国